Także o ile nie ma jakiejś innej blokady np na przepustowości kartridża czy w innym miejscu które mi nie przychodzi do głowy, mogliby dać miejsce na 64 sprajty. 256 bajtów ramu to chyba nie zrobi różnicy w nowoczesnym układzie FPGA.

Procesor PPU nie ma żadnej wewnętrznej pamięci (nie licząc tych 256 bajtów pamięci OAM).

Podczas generowania linii obrazu, musi on na bieżąco sprawdzać, jakie kafelki tła oraz jakie kafelki sprite-ów na tej linii obrazu nalezy "wyświetlić"

W tym celu sięga on do nametables (zwykle pamięc RAM w konsoli) aby odczytać, jakie kafelki tła (=jakie numery) maja się znaleźć.

Potem sięga do Pattern Tables (zwykle pamięć ROM/RAM w kartridżu) aby pobrać dane graficzne tych kafelków.

Schemat działania PPU jest zawsze taki sam, tzn. w kazdym cyklu ma dokładnie zaplanowane, jaką komórkę pamięci ma odczytać aby te informacje pobrać.

https://www.nesdev.org/wiki/PPU_renderingW cyklach `257-320` dokonuję odczytów z pamięci pattern tables, aby pobrac dane graficzne 8 sprite-ów które ma wyświetlić.

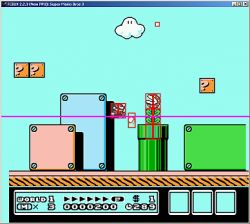

Gdybyśmy nagle chcieli wyświetlać więcej spriteów niż 8, to nie ma gdzie upchnąc tych dodatkowych cykli odczytu, które PPU musiałby wykonać aby pobrać dane o dodatkowych spriteach.

Wszystkie konsole od oryginalnych Nesów/Famicomów, po późniejsze klony na pojedynczym scalaku (UM6561=iq502 rev 2), glucie (terminator, sp60) czy współcezsne klony zachowują się IDENTYCZNIE jak pierwowzór (NES/FAmicom). Dlaczego?

Niektóre mappery (tylko MMC5) dokładnie śledzą cykl po cyklu co robi PPU aby m.in. wykrywać kolejne linie obrazu (potrzebne do zgłaszania przerwań).

Inne mappery śledzą np. tylko ile razy w "zmienia" się stan linii PPU A12 (8 razy) lub PPU A13 (43 razy o ile dobrze pamiętam) aby zliczać linie obrazu. Jeśli dodamy "dodatkowe" cykle odczytu aby sięgać po dodatkowe spritey, wszystkie dotychczasowe zależności obrazu sie rozjadą.

W wielu emulatorach jest opcja `allow more than 8 sprites per scanline`, bo emulator ma wszystkie te dane graficzne w pamięci i mu nie robi różnicy, czy wyświetla tylko 8 czy więcej spriteów (=nie musi fizycznie sięgać do pamięci po te dane tak jak PPU).

Nie wiem jak działa opisywany w tym temacie projekt (nie czytałem szczegółów), ale ten układ FPGA Lattice który jest jego sercem mui trzyać gdzieś wewnątrz kopie pattern tablesów, aby do nich nie sięgać z kartridża, albo musi robić jakieś czary.

Ja to bym w ogóle nie ruszał konsoli, preferowałbym stworzyć rozwiązanie w postaci kartridża-adaptera z którego wystawałby tylko przewód (albo gniazdo) video.

Kiedyś się za coś takiego zabierałem, jakiś prototyp nawet stworzyłem, ale kłopot był z synchronizacją drugiego PPU (=tego w adapterze) z tym w konsoli. Gdybym miał do dyspozycji jakieś pętle zegarowe może by się udało.

https://forums.nesdev.org/viewtopic.php?t=19033